A STABLE 2-26.5 GHz TWO-STAGE DUAL-GATE DISTRIBUTED MMIC AMPLIFIER

Jerry Orr

Hewlett-Packard Company, Microwave Technology Div.

1412 Fountaingrove Pkwy., Santa Rosa, CA 95401

Abstract

A 2 to 26.5 GHz monolithic distributed amplifier with  $18.75 \pm 1.25$  dB of gain, better than 12 dB return losses at input and output, and greater than 40 dB of isolation has been realized on a single 3.02mm x 1.62mm chip.

Introduction

Distributed amplifiers in MMIC form have demonstrated very wide bandwidth performance [1,2,3,4]. In addition, distributed amplifiers are capable of very good input and output matches, excellent flatness, and, thus, cascadable. They are also less sensitive to process parameter variations than reactively matched amplifiers, which makes them especially suitable for monolithic intergration.

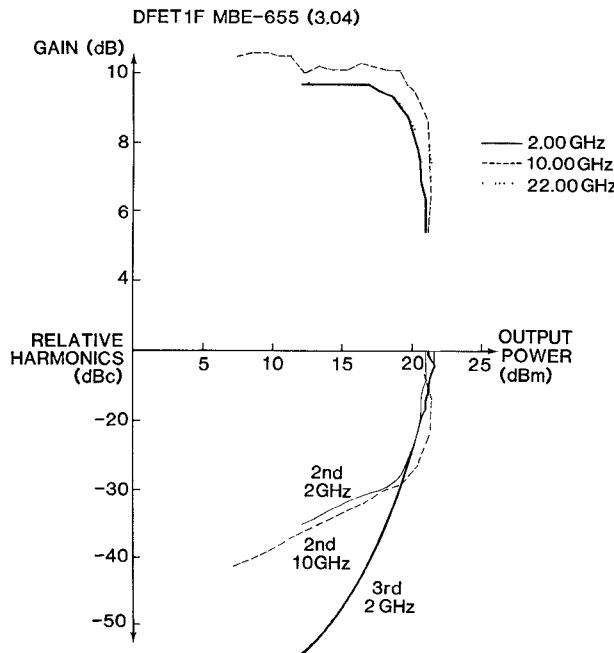

**Fig. 1** Gain Compression and Relative Harmonics of a DFET1F.

Circuit Performance

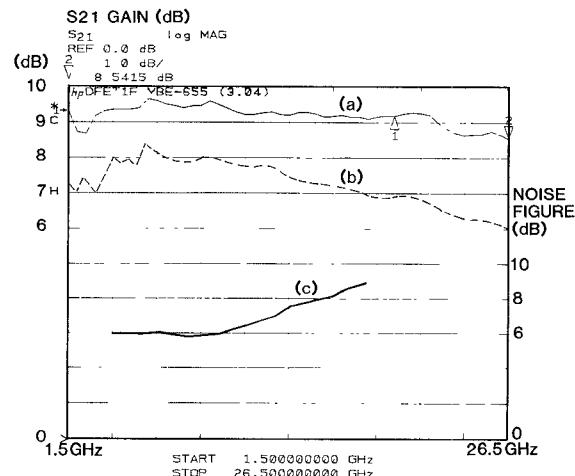

The gain of a single stage dual-gate distributed amplifier (called DFET1F) was measured to be  $9 \pm .5$  dB from 1.5 to 26.5 GHz with 19 dBm of output power with better than 25 dBc harmonics at the 1dB of gain compression point. The saturated output power was 21 dBm, as shown in Fig. 1. The noise figure of a DFET1F stage biased at 48% of  $I_{dss}$  was less than 9.3 dB, with an associated gain of 8 to 7 dB from 4 to 18 GHz, however the associated gain dropped to 6 dB at 26.5 GHz. The small signal gain and noise figure of the single stage DFET1F are shown in Fig. 2.

**Fig. 2** Gain and Noise Figure of a single DFET1F.

(a) Gain at  $V_{DD} = 5.5$  Volts,  $I_{DD} = 157$  mA

(b) Gain at  $V_{DD} = 5.5$  Volts,  $I_{DD} = 75$  mA

(c) NF at  $V_{DD} = 5.5$  Volts,  $I_{DD} = 75$  mA

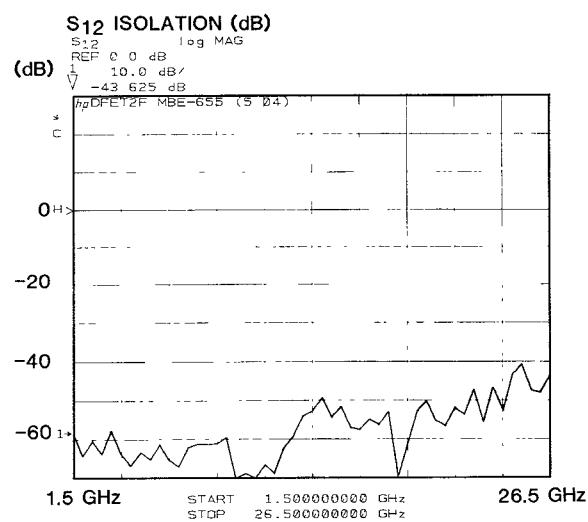

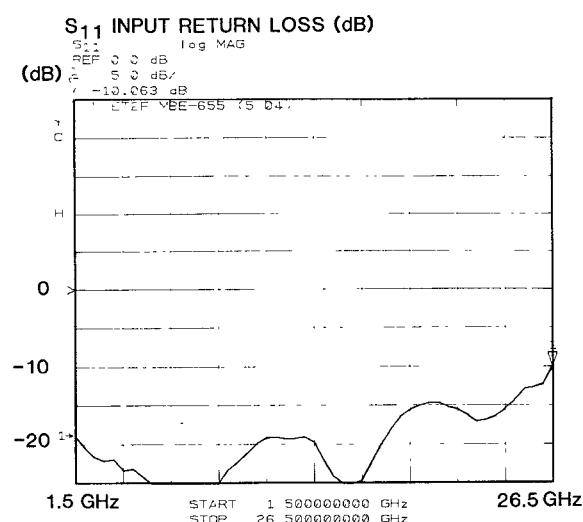

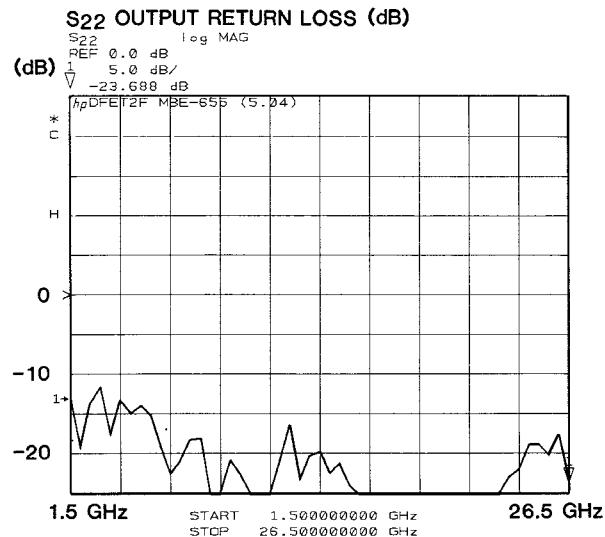

A dual-gate, two-stage distributed amplifier (called the DFET2F) has been fabricated in which a gain of  $18.75 \pm 1.25$  dB has been achieved from 1.5 to 26.5 GHz, with input and output return losses better than 12 dB, and greater than 40 dB of isolation.

#### Bias Conditions

$$V_{DD_A} = V_{DD_B} = 5.5 \text{ Volts}, \quad I_{DD_A} + I_{DD_B} = 328 \text{ mA}$$

$$V_{G1_A} = V_{G1_B} = 0 \text{ Volts}, \quad V_{G2_A} = V_{G2_B} = 2.0 \text{ Volts}$$

**Fig. 3** The four measured S-parameters of a DFET2F amplifier, measured on the wafer, with a Cascade-Microtech Model 42 probe station, connected to a Hewlett-Packard 8510A Network Analyzer.

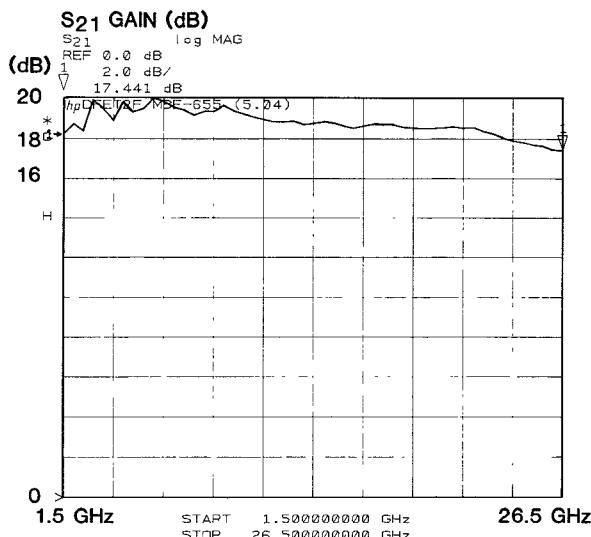

The chart and table of Fig. 4 compares these results to previous results in the 2 to 30 GHz range. A 4 dB gain single chip distributed amplifier with flat gain to 40 GHz has been reported [4], using  $.25 \mu\text{m}$  gates with the same circuit as in reference [2].

Fig. 4 Gain of MMIC distributed amplifiers.

The DFET2F amplifier has a significantly higher gain for this size chip than any previously reported result. It consists of two identical DFET1F single stage sections cascaded in series.

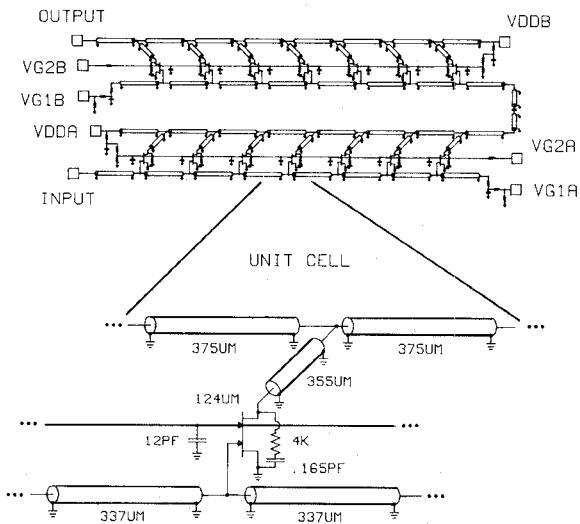

#### Circuit Design

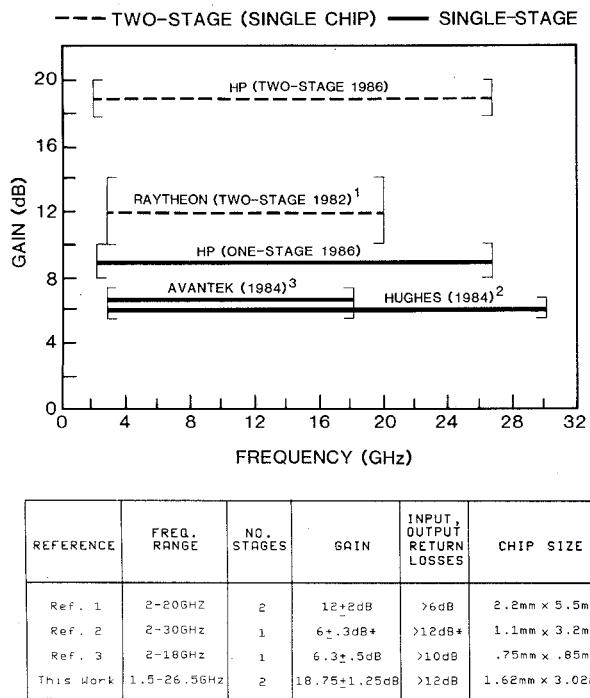

The design process of a DFET1F initially followed a procedure similar to those presented in previous works [5,6]. A cutoff of 32 GHz was chosen to assure performance to 26.5 GHz with FET parameter variations and temperature extremes. The design uses seven identical dual-gate FETs per stage, where the gate dimensions are  $124 \mu\text{m}$  by  $0.4 \mu\text{m}$ . Once the basic amplifier was designed, it was simulated on Super-Compact [9], with the length of the drain peaking line varied to compensate for losses along the gate line. Both the gate and the drain lines are terminated with  $50 \Omega$  thin-film resistors in series with on-chip bypassing capacitors. On-chip biasing networks bias the first gates to ground through a  $1 \text{ k}\Omega$  resistor, and the second gates to  $0.36 \cdot V_{DD}$  when external gate biases are not provided. Two DFET1F stages are coupled by a  $12 \text{ pF}$  capacitor shaped as a  $50 \Omega$  transmission line, to form a DFET2F amplifier. The layout of the DFET2F amplifier chip is shown in Fig. 5.

Fig. 5 DFET2F chip layout  $3.02 \text{ mm} \times 1.62 \text{ mm}$ .

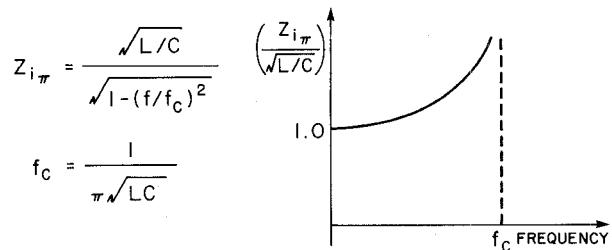

Using dual-gate FETs gives 2 dB higher gain, and 6 dB more reverse isolation per stage [3]. However, previous experimental results with cascode distributed amplifiers had a tendency to oscillate near the cutoff frequency of the gate and drain artificial delay lines. The cascode pair is unstable when loaded with large inductive reactances at both the gate and the drain. Fig. 6 [7,8] shows the increase in impedance at the capacitor nodes of an artificial delay line filter, leading to instability.

Fig. 6 Pi-section image impedance of an artificial delay line low-pass filter.

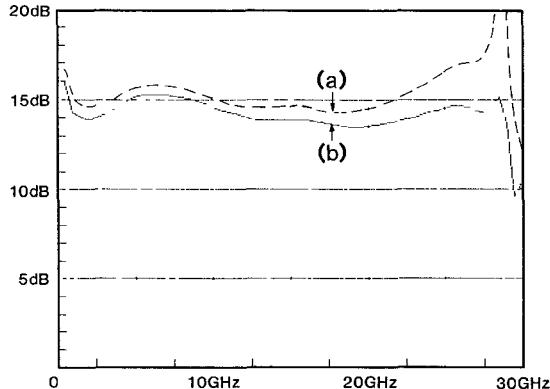

Fig. 7 DFET2F circuit schematic.

This problem has been solved by adding a simple R-C network in shunt with the drain of the common-gate FET, as shown in Fig. 7. The 4 k $\Omega$  resistor eliminates the drain line resonance near the cutoff frequency, and improves the gain flatness over the high end of the band, as shown by the computer simulation of Fig. 8. Without the 4 k $\Omega$  resistor (trace (a) in Fig. 8), the minimum stability K-factor was -29, and  $|S_{22}|$  was 1.9 at 30 GHz. With the 4 k $\Omega$  resistor (trace (b)), the minimum stability K-factor was 20, and  $|S_{22}|$  was .56 at 30 GHz.

### S21 COMPUTER SIMULATION

**Fig. 8** Effect of damping resistor on gain flatness, (a) without 4 k $\Omega$  resistor (b) with 4 k $\Omega$  resistor.

Although the FET model used for the original design simulations had an  $f_t$  of 19 GHz, process improvements resulted in a FET with an  $f_t$  of 23 GHz, thereby accounting for the higher measured gain [10].

### Circuit Fabrication

The MMIC process used for fabrication of the distributed amplifier described here is similar to a previously reported process [11], except for the following added features. The gate length is nominally 0.4  $\mu$ m and patterned using deep-UV exposure [12]. The active layer was doped at  $2 \cdot 10^{17}/\text{cm}^3$  grown using MBE. The  $f_t$  measured on a typical FET is 23 GHz. In addition, tantalum nitride thin-film resistors are available (25 ohms/square), as well as backside VIAs. The wafers are undoped LEC and 100  $\mu$ m thick at the end of the process.

### Conclusions

A two-stage, seven-section, dual-gate monolithic GaAs distributed amplifier with high gain and excellent flatness has been realized on a single MMIC chip. The instability problem associated with the cascode configuration has been solved, thereby allowing the superior gain and isolation properties of the dual gate FET to be utilized in distributed amplifiers.

### Acknowledgments

I would like to acknowledge, D. Feenan, B. Hahn, T. Noguchi, D. Schram, D. D'Avanzo, V. Makker, and T. Taylor for wafer fabrication and process development, and thank R. Fisher, D. Hornbuckle, and H. Kondoh for their technical assistance. I would especially like to thank D. Estreich for his encouragement, guidance, and advice on this project.

### References

- [1] Y. Ayasli, R. L. Mozzi, J. L. Vorhaus, and L. Hanes, "Monolithic 2-20 GHz GaAs Traveling-Wave Amplifier," *Elect. Lett.*, Vol. 18, July 1982, pp. 596-597.

- [2] J. M. Schellenberg, H. Yamasaki, and P. Asher, "2-30 GHz Monolithic Distributed Amplifier," *IEEE GaAs IC Symposium Tech. Dig.*, October 1984, pp. 77-79.

- [3] W. Kennan, T. Andrade, and C. Huang, "A Miniature 2-18 GHz Monolithic GaAs Distributed Amplifier," *IEEE 1984 Microwave and Millimeter-Wave Monolithic Circuits Symposium Digest of Papers*, May 1984, pp. 41-44.

- [4] R. G. Pauley, P. G. Asher, J. M. Schellenberg and H. Yamasaki, "A 2 to 40 GHz Monolithic Distributed Amplifier," *IEEE GaAs IC Symposium Tech. Dig.*, November 1985, pp. 15-17.

- [5] J. B. Beyer, S. N. Prasad, R. C. Becker, J. E. Nordman, and G. K. Hohenwarter, "MESFET Distributed Amplifier Design Guidelines," *IEEE Trans. MTT*, Vol. MTT-32, March 1984, pp. 268-275.

- [6] Y. Ayasli, R. L. Mozzi, J. L. Vorhaus, L. D. Reynolds, and R. A. Pucel, "A Monolithic GaAs 1-13 GHz Traveling-Wave Amplifier," *IEEE Trans. MTT*, Vol. MTT-30, July 1982, pp. 976-981.

- [7] O. J. Zobel, "Transmission Characteristics of Electric Wave-Filters," *Bell Syst. Tech. J.*, Vol. 3, 1923, pp. 567-620.

- [8] M. S. Chausi, *Principles and Design of Linear Active Circuits*, New York, McGraw-Hill, 1965, pp. 338-339.

- [9] *Super-Compact User Manual*, Vers. 1.6/1.7, Compact Software, March 1, 1984.

- [10] H. Kondoh, "An Accurate FET Modelling from Measured S-Parameters," *IEEE MTT-S Digest*, June 1986.

- [11] R. L. Van Tuyl, V. Kumar, D. C. D'Avanzo, T. W. Taylor, V. E. Peterson, D. P. Hornbuckle, R. A. Fisher, and D. B. Estreich, "A Manufacturing Process for Analog and Digital Gallium Arsenide Integrated Circuits," *IEEE Trans. MTT*, Vol. MTT-30, July 1982, pp. 935-942.

- [12] T. W. Taylor, and D. C. D'Avanzo, "A Sub-500nm Optical Lithography Gate Process for GaAs MMIC's," submitted to the Electrochemical Society SOTAPCOCS IV Symposium, held in Boston, MA, May 4-9, 1986.